- 1830 views

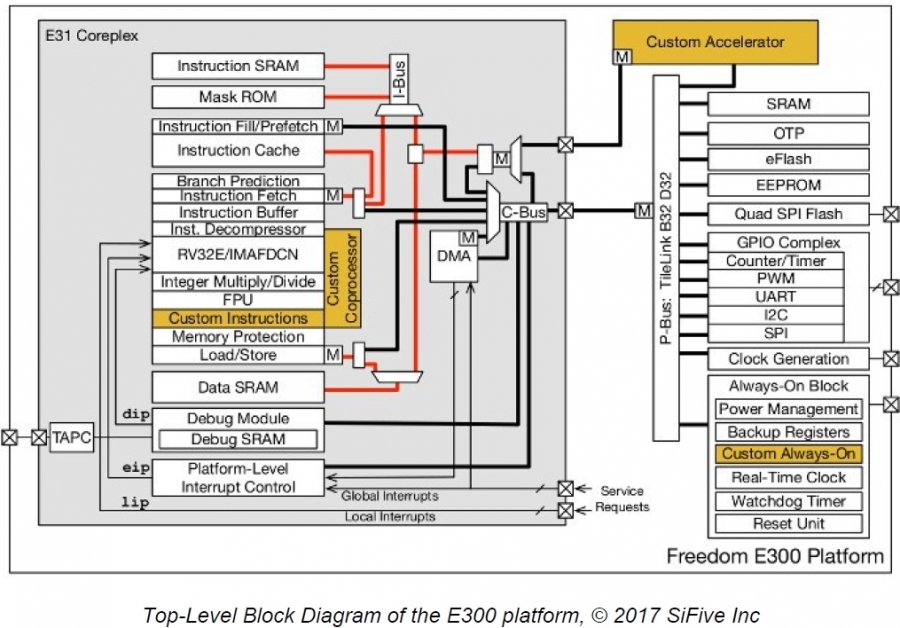

La platine Arty A7-100T renferme un FPGA Xilinx XC7A100T qui est un des FPGA les plus performant utilisé sur les Arty A7. Cette platine est idéale pour le déploiement de processeurs à cœur logiciel (softcore). Ces processeurs peuvent être propriétaires ou open source. L'un des processeurs open source les plus populaires est le RISC-V. Ce didacticiel couvre la construction d'un processeur RISC-V, en particulier le SiFive Freedom E310. Ce guide décrit le processus de chargement du Freedom E310 sur une platine Arty A7 et sa programmation à l'aide de l'IDE Arduino.

Nécessaire pour la réalisation de ce didacticiel:

- Une platine Arty A7-100T

- Un programmateur Olimex ARM-USB-TINY-H USB

- Vivado 2017.1 – Webpack Edition

- L'environnement de développement Arduino

- 10 straps souples pour assurer la connexion entre le programmateur et un des connecteur Pmod de la platine Arty qui est connecté au port JTAG Test Access du processeur

- Une machine de développement Linux ou une machine virtuelle est nécessaire pour compiler le processeur, générer le bitstream et charger l'application dans le processeur.

Installez ce qui suit sur la machine de développement Linux:

1 - Git - La commande suivante peut être utilisée:

sudo apt-get install git

2 - Device Tree Compiler - La commande suivante peut être utilisée:

sudo apt-get install device-tree-compiler

3 - Java Run Time Environment - La commande suivante peut être utilisée::

sudo apt-get install default-jre

4 - JAVAC installed - La commande suivante peut être utilisée::

sudo install openjdk-8-jdk

5 - Assurez-vous que la variable d'environnement JAVA_HOME est définie

Début de la procédure:

Téléchargez et installez la version 2017.1 de Vivado. Une fois téléchargé, ouvrez une fenêtre de terminal. Ensuite, pour ce didacticiel, changez le répertoire (cd) en répertoire personnel. Cette fenêtre de terminal sera utilisée pour construire le processeur RISCV.

Configurez Vivado en recherchant le script de paramètres dans la ligne de commande du terminal, à l'aide de la commande suivante:

source /opt/Xilinx/Vivado/2017.1/settings64.sh

Remarque: Si vous utilisez un environnement Linux 32 bits, sourcez le script settings32.sh à la place.

Téléchargez et incluez les fichiers de la carte Digilent afin que Vivado puisse les utiliser. Utilisez git pour télécharger les fichiers de définition de carte à partir du référentiel Digilent à l'aide de la commande suivante:

git clone https://github.com/Digilent/vivado-boards.git

Une fois téléchargé, copiez les «nouveaux» fichiers de la carte dans le répertoire Vivado approprié. Ceci peut être réalisé avec la commande suivante:

sudo cp -r vivado-boards / new / board_files / * /opt/Xilinx/Vivado/2017.1/data/boards/board_files/

Il est maintenant possible de générer le processeur et l'implémentation FPGA.

Construire le RISC-V

La génération et l'implémentation du processeur peuvent être effectuées en exécutant Makefiles.

Tout d'abord, téléchargez le processeur de liberté SiFive en utilisant git et en clonant son référentiel:

git clone --recursive https://github.com/sifive/freedom.git

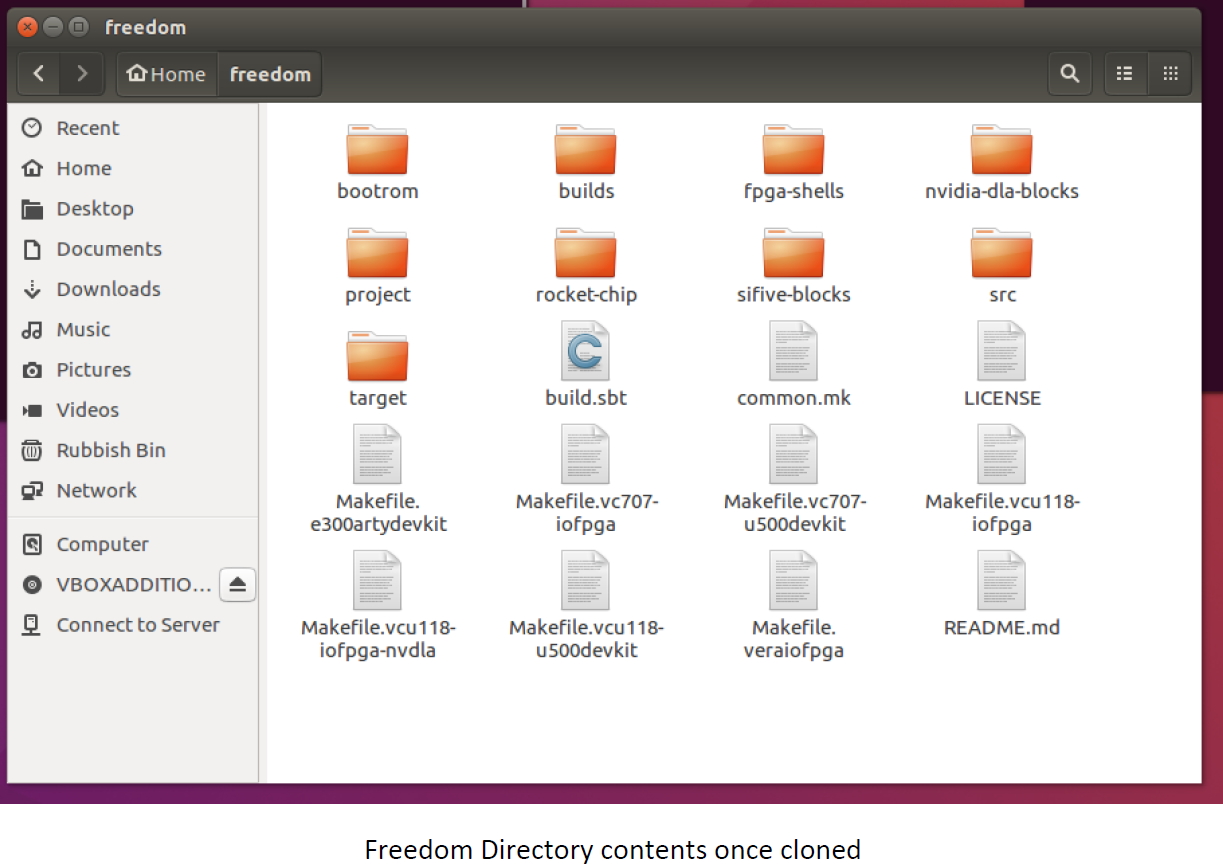

Le clonage prendra un certain temps en raison du grand nombre de fichiers à télécharger. Une fois téléchargé, un nouveau dossier appelé «Freedom» peut être vu dans le répertoire de travail.

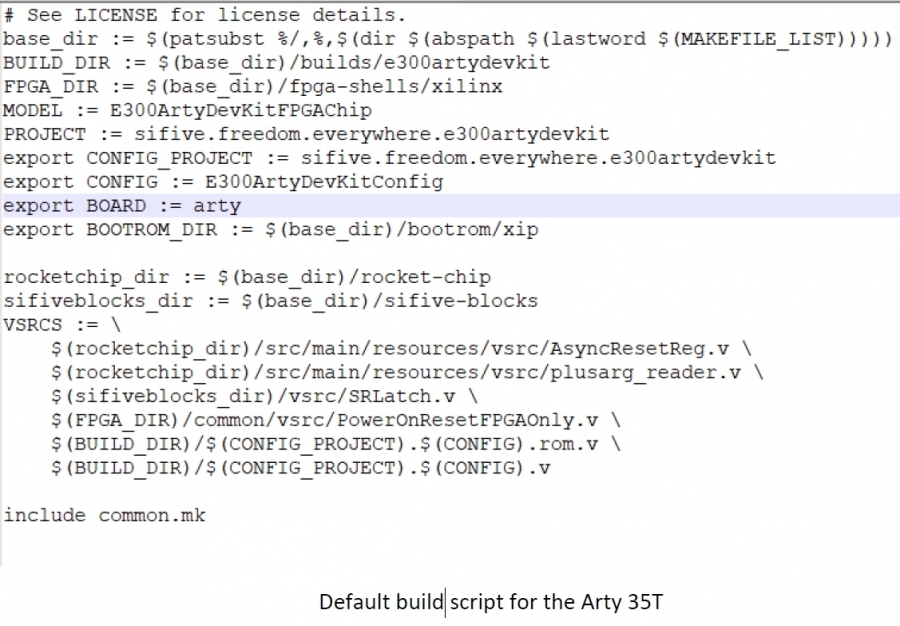

Dans ce répertoire, il existe plusieurs Makefiles. Ce didacticiel utilisera l'exemple Makefile.e300artydevkit. L'exemple de script générera le processeur RISC-V pour les cartes Arty A7-35T et Arty A7-100T. La chaîne d'outils doit d'abord être compilée.

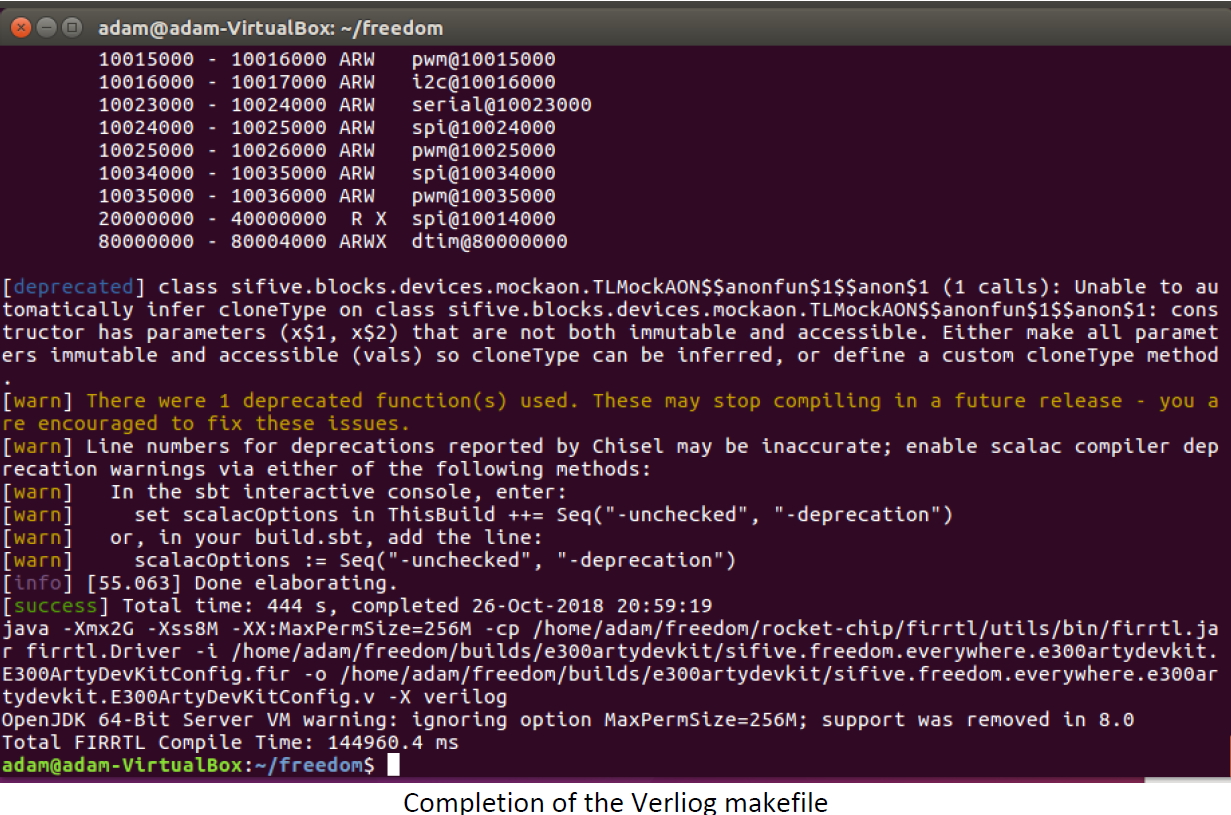

Dans la fenêtre du terminal, remplacez le répertoire de travail par le répertoire des chaînes d'outils dans rocket-chip / riscv-tools et exécutez le script build.sh. Cela créera la chaîne d'outils nécessaire à la génération des fichiers d'implémentation. Pour générer l'instanciation Verilog du processeur à partir des fichiers Chisel HDL, exécutez la commande suivante:

make -f Makefile.e300artydevkit Verilog

La compilation des fichiers prendra un peu de temps. La génération de fichiers Verilog génériques permettra de cibler la carte Arty A7-35T ou Arty A7-100T.

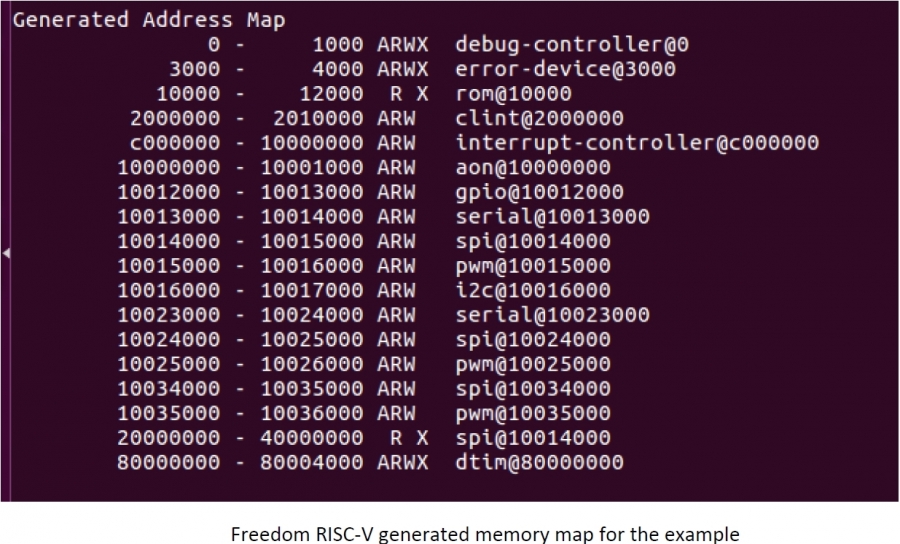

Dans la fenêtre du terminal, les périphériques et leurs emplacements dans la carte mémoire sont visibles.

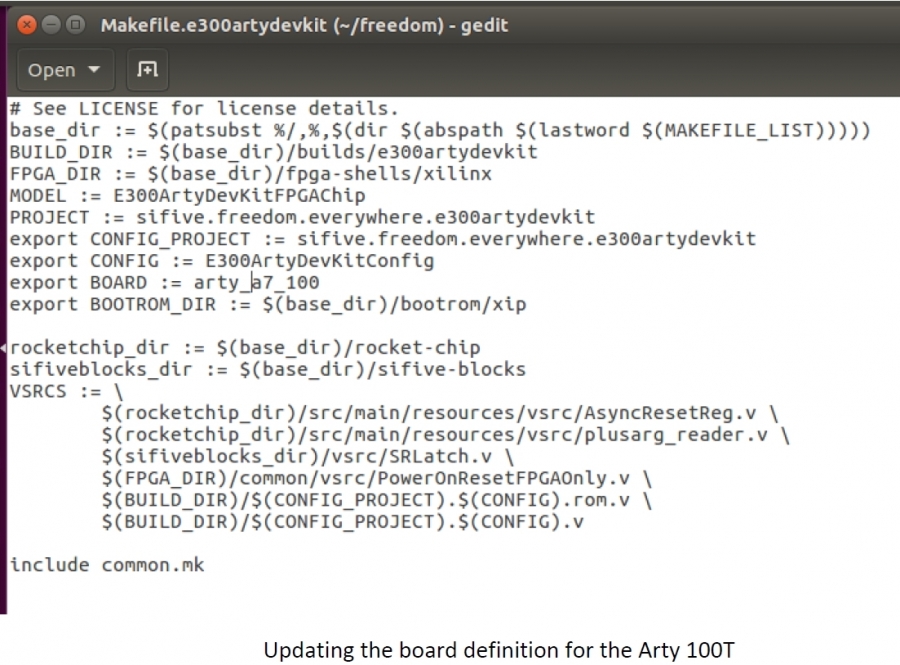

Avec la description Verilog du processeur disponible, l'étape suivante consiste à décider laquelle des cartes Arty sera ciblée. Aucune modification ne doit être apportée si vous ciblez l'Arty A7-35T. Si vous ciblez l'Arty A7-100T, quelques ajustements mineurs doivent être effectués. Pour effectuer ces modifications, ouvrez le makefile Makefile.e300artydevkit à l'aide d'un éditeur de texte et changez le type de carte. Par défaut, le Makefile générera l'implémentation FPGA pour l'Arty A7-35T.

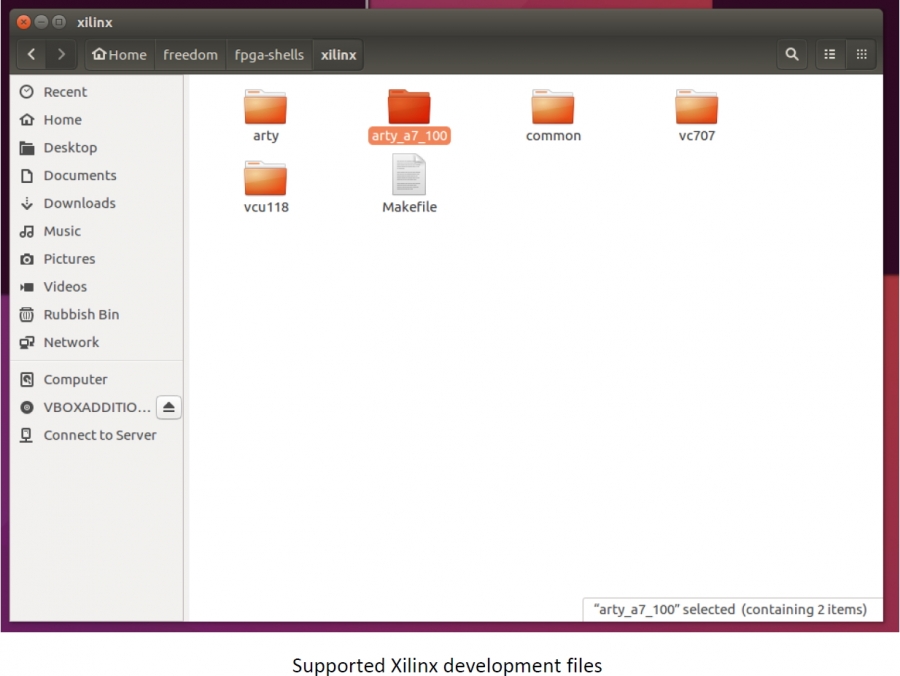

Pour générer une implémentation pour l'Arty A7-100T, changez le type de carte en arty_a7_100T. Ouvrez un navigateur de fichiers et accédez au répertoire freedom / fpga-shells / Xilinx. Plusieurs dossiers, nommés pour chaque carte de développement prise en charge, peuvent être vus ici. Notez que le nom du dossier arty_a7_100 correspond au type de carte utilisé.

De retour dans l'éditeur de texte avec le Makefile, changez le nom de la carte en arty_a7_100.

Enregistrez et fermez le fichier modifié.

Avec cela, l'implémentation FPGA peut maintenant être générée. Dans la fenêtre du terminal, exécutez la commande suivante:

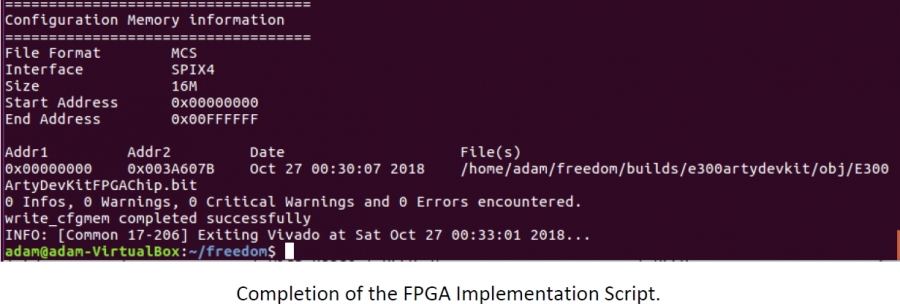

make -f Makefile.e300artydevkit mcs

Cela prendra du temps, car le script utilisera Vivado et la chaîne d'outils RISC-V pour générer à la fois un flux binaire et un fichier MCS. Le fichier MCS peut être programmé dans la mémoire flash de l'Arty A7 100T et charger le processeur RISC-V lorsque la carte est sous tension.

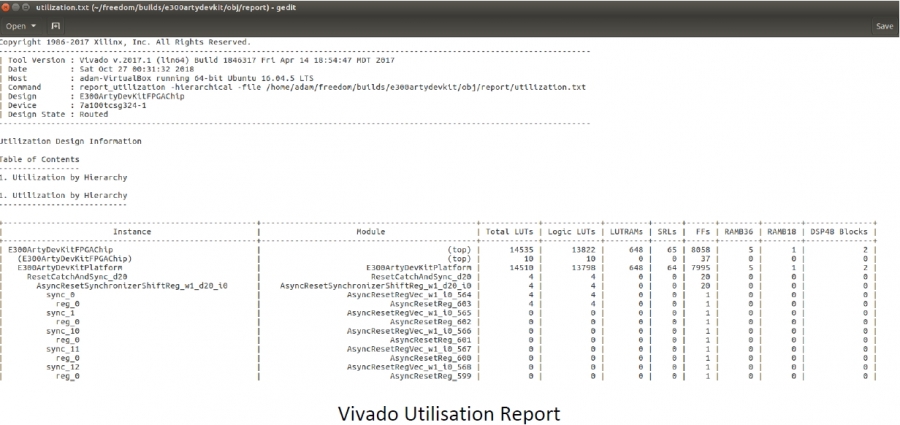

Les fichiers de sortie seront disponibles sous le répertoire:

<workspace>/freedom/builds/e300artydevkit/obj

Les fichiers BIT, les fichiers MCS et les rapports d'implémentation de Vivado peuvent tous être trouvés ici.

Programmation du matériel

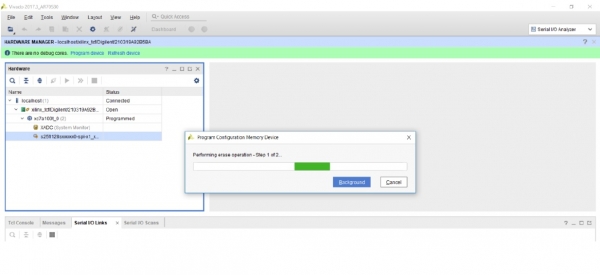

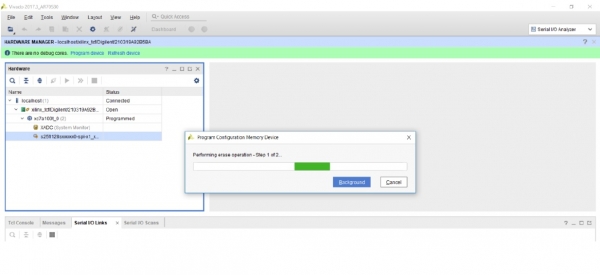

Avec le fichier de programmation disponible, l'étape suivante consiste à programmer la mémoire flash à l'aide de Vivado.

Ouvrez Vivado à l'aide de la commande: «Vivado».

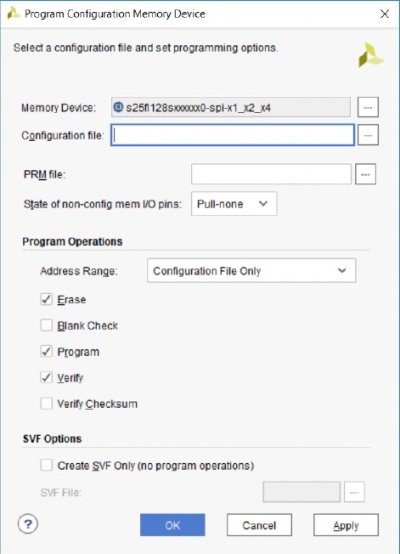

Une fois l'interface graphique démarrée, l'étape suivante consiste à connecter l'Arty A7-100T à la machine de développement via le port micro USB (J10) et à ouvrir le gestionnaire de matériel de Vivado. Une fois la carte connectée, l'onglet matériel à gauche de l'écran affiche le périphérique FPGA. Sélectionnez le périphérique, puis faites un clic droit dessus et sélectionnez * Ajouter un périphérique de mémoire de configuration *. Cela ouvrira une boîte de dialogue où le type de mémoire peut être sélectionné. L'Arty A7-100T est équipé d'un dispositif Spansion S25FL128xxxxx.

Après avoir sélectionné le périphérique, une invite de dialogue vous demandera si le périphérique doit être programmé maintenant. Cliquez sur Oui et une autre boîte de dialogue s'ouvrira.

Sélectionnez le fichier MCS généré et l'appareil sera programmé. Une fois ce processus terminé, l'Arty A7-100T exécutera le processeur RISC-V. Vérifiez que les cavaliers de l'Arty A7 sont configurés de manière à pouvoir être programmés à partir du flash et appuyez sur le bouton de réinitialisation.

Confirmez que le processeur fonctionne en procédant comme suit:

Appuyez sur le bouton 3 et voyez la LED 6 s'éteindre

Appuyez sur le bouton de réinitialisation et voyez la LED 4 s'éteindre

Cependant, une application personnalisée doit encore être créée et téléchargée. Cela peut être réalisé en utilisant l'environnement de développement Arduino.

Génération de logiciels

Tout d'abord, le pod Olimex JTAG doit être connecté au port Pmod D de l'Arty A7, ce qui permet de télécharger et de déboguer des programmes à l'aide de l'interface JTAG. La brochage pour connecter les deux peut être trouvée ici.

Avec cela, une application personnalisée peut maintenant être développée. La meilleure façon de commencer à programmer le RISC-V est d'utiliser l'environnement de développement Arduino.

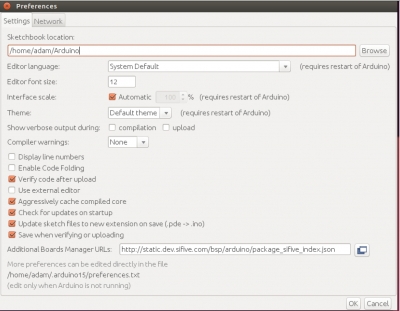

L'installation de la prise en charge du processeur SiFive Freedom est facile. Sous «Fichier → Préférences», pointez l'URL du gestionnaire de cartes supplémentaires vers l'URL suivante:

http://static.dev.sifive.com/bsp/arduino/package_sifive_index.json

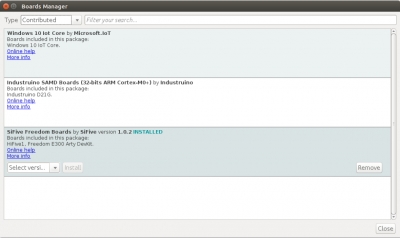

L'étape suivante consiste à installer la carte à l'aide du gestionnaire de carte trouvé dans le menu «Outils → Cartes».

Dans la boîte de dialogue Board Manager, sélectionnez le type Contributed pour trouver les SiFive Freedom Boards.

Une fois celui-ci installé, des applications peuvent être développées et des exemples d'applications chargés, tout comme pour n'importe quelle autre carte dans cet environnement. N'oubliez pas de sélectionner le kit de développement Freedom Arty dans la liste de sélection des cartes.

Dépannage

1. Assurez-vous que les pilotes de câble Xilinx sont installés. Ceci peut être réalisé en changeant d'abord le répertoire en

<Installation xilinx> Vivado / 2017.1 / data / xicom / cable_drivers / lin64 / install_script / install_drivers

Puis exécutez la commande:

sudo ./install_drivers

2. Assurez-vous que le Olimex USB dispose des autorisations requises. Modifiez le fichier suivant:

/etc/udev/rules.d/99-openocd.rules

En ajoutant les éléments suivants:

# These are for the Olimex Debugger for use with E310 Arty Dev Kit

SUBSYSTEM=="usb", ATTR{idVendor}=="15ba", ATTR{idProduct}=="002a", MODE="664",

GROUP="plugdev"

SUBSYSTEM=="tty", ATTRS{idVendor}=="15ba", ATTRS{idProduct}=="002a", MODE="664",

GROUP="plugdev"

Enregistrez et entrez la commande sudo udevadm control –reload-rules

3. Si des problèmes surviennent lors du téléchargement, vérifiez les connexions entre Olimex et Pmod Port D, et assurez-vous que l'utilisateur est membre du groupe plugdev.

Prochaines étapes

Pour plus de guides sur la façon d'utiliser l'Arty A7, visitez le centre de ressources de Digilent.

Pour plus d'informations sur Vivado, consultez les didacticiels Vivado de Digilent.

Pour le support technique, veuillez visiter la section FPGA des forums Digilent.